## New Release

## **LTEC Corporation**

Your most experienced partner in IP protection

## MULTI-CELL BATERY MONITOR ASIC BY DESNO FOR TOYOTA PRIUS ZVW51 -- DETAILED SCHEMATIC ANALYSIS REPORT

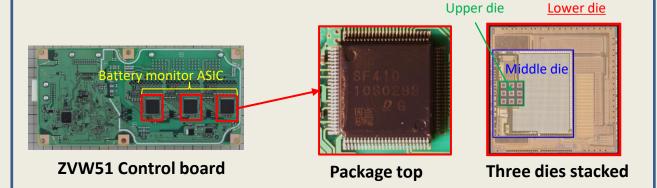

June, 2016. This 230 page document is one of six reports, each analyzing various segments of the ZVW51 system. This report is focusing on the multi-cell battery monitor ASIC and its detailed schematic analysis. Three dies are stacked in one package. The upper die is not connected eclectically. The function of the middle die is daisy chain communication, voltage reference and biasing, while the lower die is a multiplexer (MUX) and Analog to digital converter (ADC).

This report is a detailed schematic analysis of the full analog circuit of the lower die and the voltage reference circuit of the middle die.

Some of the key features are:

- 1. All necessary bias or reference voltages for the lower die are derived from the middle die.

- 2. Although BCDMOS (Bipolar, CMOS and LDMOS) process is used, the circuit is configured by CMOS transistors only.

- 3. Switch transistors for cell balancing are built-in and the circuitry for the lower 4 cells and the upper 16 cells are different.

Specific segments of the report are available with proportional pricing.

Note: The listed report price may not be accurate as it decreases over time. Please contact us for current report pricing: info@ltecusa.com

15G-0005-1

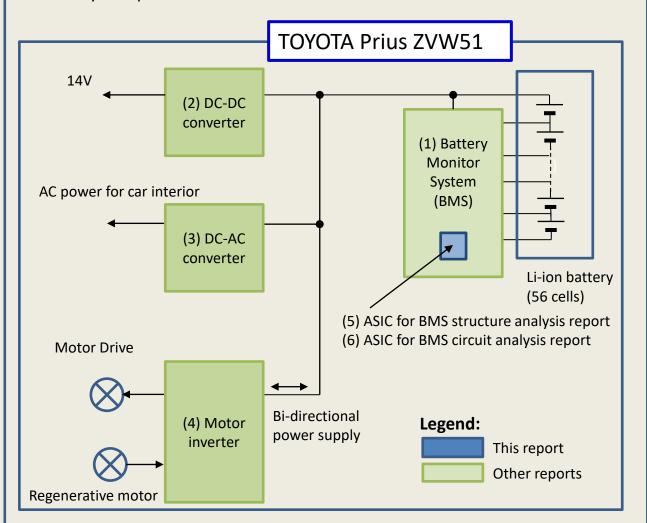

Phone: (408) 432-7247 www.ltecusa.com Contact: info@ltecusa.com The block diagram of the Toyota Prius ZVW51 system and the corresponding LTEC analysis reports are listed below:

| Family of LTEC analysis reports related to the ZVW51 system | Report No. |

|-------------------------------------------------------------|------------|

| 1. BMS PCB circuit analysis report analysis report          | 15G-0006-1 |

| 2. DC-DC converter PCB circuit analysis report              | 15G-0007-1 |

| 3. DC-AC converter PCB circuit analysis report              | 16G-0001-1 |

| 4. Motor-inverter PCB circuit analysis report               | 15G-0008-1 |

| 5. ASIC for BMS structure analysis report                   | 15G-0013-1 |

| 6. ASIC for BMS circuit analysis (this report)              | 15G-0005-1 |

15G-0005-1

## **Table of Contents**

|    |                                      | Page |

|----|--------------------------------------|------|

| 1. | Device summary                       | 8    |

| 2. | Product outline                      | 9    |

| 3. | Pin assignment                       | 19   |

| 4. | Elements detail in die               | 22   |

| 5. | Analysis area                        | 35   |

| 6. | Schematic detail (bottom die)        | 37   |

| 7. | Schematic detail (middle die) (Note) | 181  |

Note: Bandgap circuit and its related circuit

15G-0005-1