# New Release

### LTEC Corporation Your most experienced partner in IP protection

## ANALYSIS REPORT OF TRANSFORM 'TPH3207WS' 650V POWER GaN FET

*April 2018.* LTEC Corporation released a detailed structure analysis report of this 650V GaN FET. This product has 50A output current capability, which is the almost double comparing with other GaN devices. This FET is a cascode arrangement using a low-voltage Si-FET device in order to realize a normally OFF configuration.

Package top view

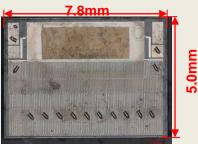

Die top view

#### Device features

- Max. operating voltage : 650V, rated DC Drain current ID=50A at Tj=25°C

- ON-resistance, RON =  $41m\Omega$

#### Key analysis results

- Actual break-down voltage BVdss=1700V. It has wide margin compared with operating voltage specification (Vdss=650)  $\rightarrow$  Twice lager than other GaN's.

- Countermeasures of device structure and layout for JEDEC compliant

- Stacked structure (GaN device and low voltage Si-FET) to fit in TO-247

- The countermeasure for Gate abnormal oscillation and ringing

- The 155 pages report includes

- 1. The comparison with other GaN power devices,

- 2. Package cross section and EDX analysis

- 3. Die plan analysis

- 4. Die cross section (SEM, TEM), epi layer TEM-EDX material analysis

- 5. Electrical characteristic measurement (Ron, leakage current-vs-temperature, break down voltage and Drain capacitance(Coss vs Vds)

Note: The listed report price may not be accurate as it decreases over time. Please contact us for current report pricing : **info@ltecusa.com**

17G-0031-1

LTEC Corporation US Representative Office No.203 2880 Zanker Road San Jose, CA 95034

# **Table of Contents**

| I. Structure Analysis                                           | Pag | ge |

|-----------------------------------------------------------------|-----|----|

| 1. Device summary, Table 1,                                     |     | 3  |

| 1.1. Executive Summary                                          |     | 4  |

| 1.2. Summary of analysis results                                |     | 5  |

| 1.3. Comparison with other makers' GaN devices                  |     | 7  |

| 2. Package analysis                                             |     | 8  |

| 2.1. X-ray observation                                          |     | 9  |

| 2.2. Cross section                                              |     | 13 |

| 3.0. Cascode arrangement/structure                              |     | 31 |

| 3.1. GaN HEMT die                                               |     | 32 |

| 3.2. Si MOSFET die                                              |     | 33 |

| 4. GaN HEMT die analysis                                        |     | 34 |

| 4.1. GaN HEMT structure analysis summary                        |     | 35 |

| Table 2. GaN HEMT device structure                              |     | 35 |

| Table 3. Process of GaN HEMT                                    | 36  |    |

| Table 4. Layer material and thickness                           |     | 36 |

| 4.2. Plan view                                                  |     | 37 |

| 4.3. Plan view (SEM)                                            |     | 58 |

| 4.4. Cross section (SEM)                                        |     | 62 |

| 4.5. Cross section (TEM)                                        |     | 69 |

| 4.6. GaN Epi structure and material analysis (SEM EDX, TEM EDX) |     | 76 |

| 4.7. Other material analysis (SEM EDX, TEM EDX)                 |     | 77 |

17G-0031-1

| II. Electrical characteristic                                       | Page |

|---------------------------------------------------------------------|------|

| 5. Evaluation                                                       | 78   |

| 5.1. Cascode Id-Vds characteritics                                  | 79   |

| 5.2. OFF-state Id-Vds and Ea(activation energy) (Note1)             | 80   |

| 5.3. OFF-state break-down voltage (GaN HEMT)                        | 81   |

| 5.4. Capacitances (Ciss, Coss, Crss) - Vds                          | 82   |

| 5.5. Ron: Correlation analysis of the GaN structural parameters and |      |

| electrical measurements.                                            | 83   |

| 5.6. Estimation of 2DEG sheet resistance and carrier concentration  | 85   |

| 6. Appendix                                                         |      |

| 6.1. EDX (Package)                                                  | 87   |

| 6.2. EDX (GaN HEMT)                                                 | 124  |

|                                                                     |      |

Note1: Device temperature is as the parameter.

17G-0031-1