Your most experienced partner in IP protection

# WOLFSPEED C3M0075120K 1,200V SIC MOSFET SHORT CIRCUIT ROBUSTNESS ANALYSIS REPORT

New

Release

*February 2020.* The short-circuit (SC) capability of power transistors, especially SiC power MOSFETs, is one of the most critical reliability-related specifications. Compared to Si-based IGBTs, the size of the SiC transistor is smaller. This leads to significant reduction in SC endurance time (tsc).

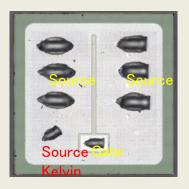

Package

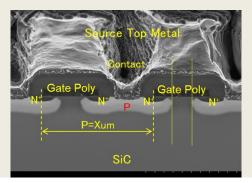

Die image

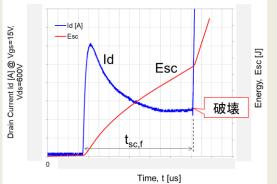

Drain current waveform and short-circuit energy (Esc)

### Abstract

This is the first published short-circuit robustness analysis report that examines the correlation between short circuit robustness and the physical structure of the C3M0075120K device, which the 3<sup>rd</sup> gen. of Wolfspeed.

### The report includes:

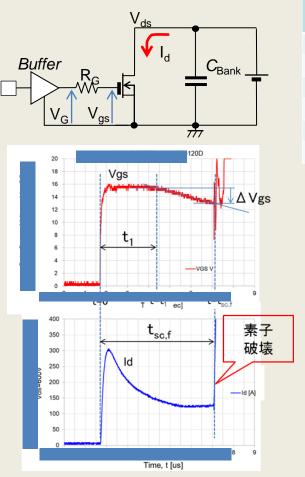

- Identification of the mechanisms limiting short-circuit capability, measurements, physical analysis results, and extraction of the critical temperature (Tj(crit)) at the onset of failure.

- Comparison of short-circuit robustness with 2nd gen 1200V SiC MOSFETs.

- Examination of the differences in semiconductor structure, process, and their effect on short circuit robustness.

- Use value of the evaluation results in this report

- The minimum response time of the short-circuit protection circuit can be estimated.

- The internal device temperature can be estimated by performing electrothermal SPICE simulation using measured short-circuit drain current waveform and endurance time (t<sub>sc. f</sub>).

Note: The report price may change over time. For current price contact info@ltecusa.com.

18G-0032-1

LTEC Corporation US Representative Office No.203 2880 Zanker Road San Jose, CA 95034

| Table of Contents                                                      |      |

|------------------------------------------------------------------------|------|

|                                                                        | Page |

| Summary                                                                |      |

| Background, purpose and executive summary                              | 3    |

| Physical analysis results                                              |      |

| Device structure and material analysis                                 | 5    |

| Table 1. Summary of each parameter                                     | 6    |

| Short circuit robustness evaluation                                    |      |

| Evaluation circuit                                                     | 7    |

| Evaluation conditions                                                  | 9    |

| Short circuit robustness evaluation results                            |      |

| Voltage and current waveforms                                          | 10   |

| Table 3. Summary of measurement results                                | 17   |

| Discussion for evaluation results                                      |      |

| Peak drain current (Isc,pk) vs. drain voltage (Vds)                    | 19   |

| Short circuit endurance time (tsc) vs. drain voltage (Vds)             | 19   |

| Short circuit energy (Esc,f) vs drain voltage (Vds)                    | 20   |

| Short circuit endurance time(tsc) vs power dissipation (Pd = Id x Vds) | 21   |

| Gate leakage current considerations during SC                          | 22   |

| Estimation of junction temperature (ΔTj) rise                          | 25   |

| Comparison of transistor structure vs 2 <sup>nd</sup> gen              | 30   |

| Conclusion                                                             | 33   |

| Appendix                                                               |      |

| References                                                             | 34   |

# **Excerpts from the report**

Fig.4: Cross-sectional image of SiC transistor

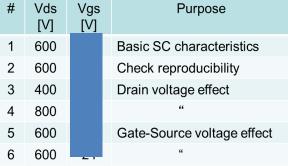

#### Table 2: Evaluation Conditions

**Fig.17**: Measured gate-source voltage and drain current waveforms during SC event.

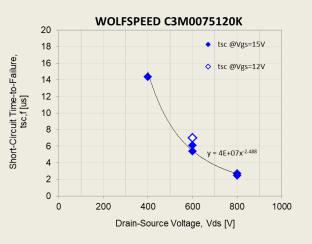

**Fig.18**: Measured dependence of the SC time to failure  $t_{sc.f}$  vs the drain voltage Vds.

LTEC Corporation US Representative Office No.203 2880 Zanker Road San Jose, CA 95034 Phone: (408) 489-1994 www.ltecusa.com Contact: info@ltecusa.com