## New Release

## **LTEC Corporation**

Your most experienced partner in IP protection

# ON SEMICONDUCTOR NVHL080N120SC1 AUTOMOTIVE CERTIFIED 1,200V SIC MOSFET SHORT CIRCUIT ROBUSTNESS ANALYSIS REPORT

**February 2020.** The short-circuit (SC) capability of power transistors, especially SiC power MOSFETs, is one of the most critical reliability-related specifications. Compared to Si-based IGBTs, the size of the SiC transistor is smaller. This leads to significant reduction in SC endurance time (test)

time (tsc).

Package Abstract

Die image

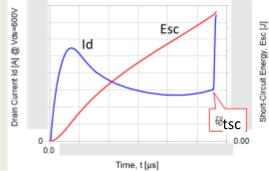

Drain current waveform and short-circuit energy (Esc)

This is the first published short-circuit robustness analysis report that examines the correlation between short circuit robustness and the physical structure of the NVHL080N120SC1 device. This device is compliant with the AEC Q101 automotive standard.

#### The report includes:

- Identification of the mechanisms limiting short-circuit capability, measurements, physical analysis results, and extraction of the critical temperature (Tj(crit)) at the onset of failure.

- Comparison of short-circuit robustness with other makers' 1,200V SiC MOSFETs. Examination

of the differences in semiconductor structure, process, and their effect on short circuit

robustness.

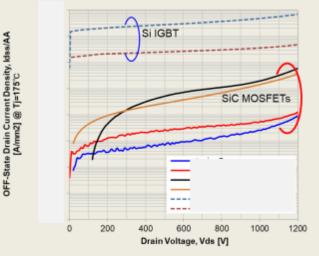

- Comparison of the electrical characteristics (off-state leakage current and temperature dependence) with other makers, and identification of differences and limitations .

#### Use value of the evaluation results in this report

- The minimum response time of the short-circuit protection circuit can be estimated.

- The internal device temperature can be estimated by performing electrothermal SPICE simulation using measured short-circuit drain current waveform and endurance time (t<sub>sc, f</sub>).

Note: The report price may change over time. For current price contact info@ltecusa.com.

19G-0007-3

Phone: (408) 489-1994 www.ltecusa.com Contact: info@ltecusa.com

## **Table of Contents**

|                                                                                | Page |  |  |

|--------------------------------------------------------------------------------|------|--|--|

| Summary                                                                        |      |  |  |

| Background, purpose and executive summary                                      |      |  |  |

| Physical analysis results                                                      |      |  |  |

| Device structure and material analysis                                         | 5    |  |  |

| Table 1. Summary of each parameter                                             |      |  |  |

| Short circuit robustness evaluation                                            |      |  |  |

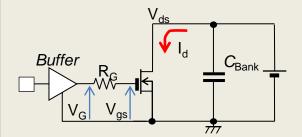

| Evaluation circuit                                                             | 7    |  |  |

| Evaluation conditions                                                          | 9    |  |  |

| Short circuit robustness evaluation results                                    |      |  |  |

| Voltage and current waveforms                                                  | 10   |  |  |

| Table 3. Summary of measurement results                                        | 17   |  |  |

| <u>Discussion for evaluation results</u>                                       |      |  |  |

| Peak drain current (Isc,pk) vs. drain voltage (Vds)                            | 19   |  |  |

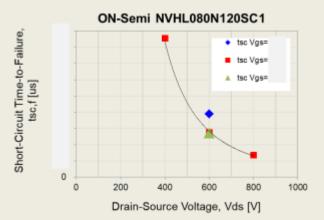

| Short circuit endurance time (tsc) vs. drain voltage (Vds)                     | 20   |  |  |

| Short circuit energy (Esc,f) vs drain voltage (Vds)                            |      |  |  |

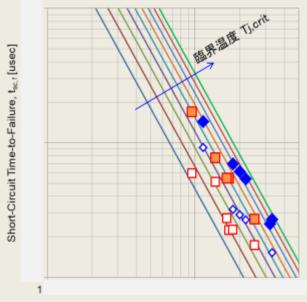

| Short circuit endurance time(tsc) vs power dissipation (Pd = $Id \times Vds$ ) |      |  |  |

| Gate leakage current considerations during SC                                  |      |  |  |

| Estimation of junction temperature (ΔTj) rise                                  | 27   |  |  |

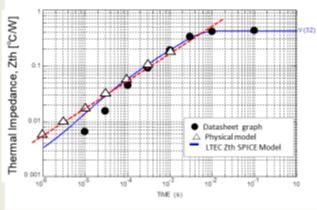

| Thermal impedance                                                              | 30   |  |  |

| Comparison of transistor structure and electrical characteristics              | 33   |  |  |

| Comparison of Onsemi's and Wolfspeed's 1,200V transistors                      |      |  |  |

| Electrical characteristic                                                      | 35   |  |  |

| Drain current at short circuit mode                                            | 37   |  |  |

| Conclusion                                                                     | 39   |  |  |

| <u>Appendix</u>                                                                |      |  |  |

| References                                                                     | 40   |  |  |

## **Excerpts from the report**

Fig.2: Die

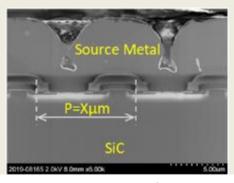

Fig.4: Cross-sectional image of SiC transistor

Table 2: Evaluation Conditions

| # | Vds<br>[V] | Vgs<br>[V] | Purpose                    |

|---|------------|------------|----------------------------|

| 1 | 600        | 20         | Basic SC characteristics   |

| 2 | 600        | 20         | Check reproducibility      |

| 3 | 400        | 20         | Drain voltage effect       |

| 4 | 800        | 20         | u                          |

| 5 | 600        | 16         | Gate-Source voltage effect |

| 6 | 600        | 24         | и                          |

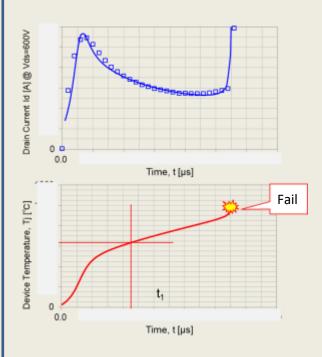

**Fig.17**: Measured gate-source voltage and drain current waveforms during SC event.

**Fig.18**: Measured dependence of the SC time to failure  $t_{sc.f}$  vs the drain voltage Vds.

### **Excerpts from the report (cont.)**

Dissipated Power Density, P<sub>d</sub>/A [W/mm<sup>2</sup>]

**Fig.28**:Measured short circuit durable time (tsc, f) vs. Power dissipation density  $Pd/A = (Vds \ x \ Id)/A$ .

Fig.29: NVHL080N120SC1 Thermal impedance plot

•: Data from datasheet,

(Blue line) Calculated using the SPICE model provided by manufacturer, and

$(\Delta)$  Calculated using the analysis result by LTEC

**Fig. 30:** Extracted transistor temperature rise using short circuit transient SPICE model

**Fig. 33:** Measured off-state drain current (@ Vgs = 0V)