## Si MOSFET(150V) : iDEAL Semiconductor SuperQ MOSFET (Super Junction) iS15M7R1S1C 構造解析レポート

パッケージ外観

Si MOSFETチップ

### レポート概要

iDEAL Semiconductorは、米国ペンシルベニア州リーハイバレーに本拠を置くファブレス半導体メーカーで、SuperQパワーMOSFETと呼ばれる製品群の量産を開始しました。

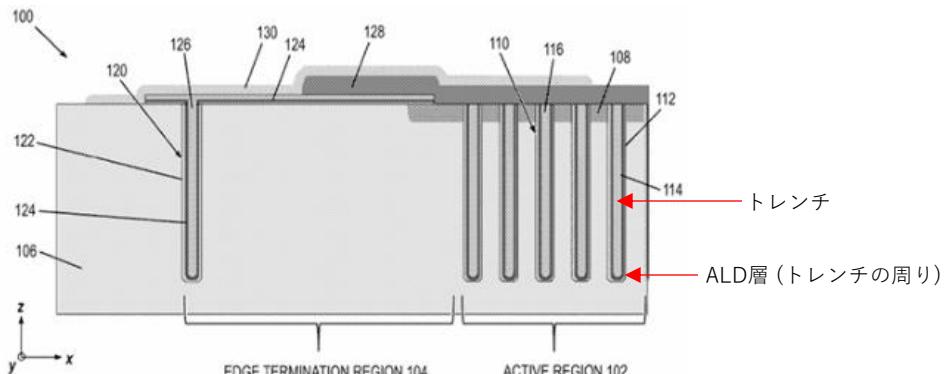

このSuperQパワーMOSFET技術は、SJ-MOSのようなリサーフ構造に由来するものであり、独自のトレンチ分離技術とドーピング濃度によってRonAAやブロッキング電圧などの主要な性能分野でワイドバンドギャップ半導体に匹敵しています。

今回は、本製品の平面解析、断面解析から構造の特徴を明らかにする構造解析レポートをリリースしました。

### 製品特徴

型番： iS15M7R1S1C  $V_{DS}=150V$ 、  $I_D=133A$ 、  $R_{DS(ON)}=5.4m\Omega$  製品リリース日：2025年6月

データシート：<https://idealsemi.com/wp-content/datasheets/iS15M7R1S1C-Datasheet.pdf>

・アプリケーション：産業オートメーション、AI データセンター、高電圧 DC 電力変換など

### 解析内容&レポート価格

構造解析レポート： 価格¥650,000 (税別) 発注後1weekで納品

・本製品のトランジスタセルは、トレンチ型ゲート構造で、トレンチの側壁にALD (Atomic Layer Deposition)層が形成されたSi SJ MOSFETです。

性能面では、本製品と同程度定格のInfineon 150V Si MOSFET(OptiMOS 5)と比較すると、本製品のRonxAAはOptiMOS 5の2/3程度になります。

・ALD層の確認には、別途SCM分析が必要となります。

詳細の内容については別途ご相談ください。

また、本製品の製造プロセスシーケンスや電気特性解析レポートも作成可能です。

ご興味がございましたら、エルテックまでお問い合わせください。

## 構造解析レポート 目次

| 【目次】 |                                        | Page      |

|------|----------------------------------------|-----------|

| 1    | デバイスサマリー                               |           |

|      | Table1-1:デバイスサマリー                      | ... 3     |

| 1-1. | 解析結果まとめ                                | ... 4     |

|      | Table1-2: デバイス構造: Si MOSFET            | ... 5     |

|      | Table1-3: デバイス構造: レイヤー材料・膜厚            | ... 6     |

|      | Table1-4: デバイス構造: 実装パッケージ構造概要          | ... 7     |

| 2    | パッケージ解析                                |           |

| 2-1. | 外観観察                                   | ... 9-10  |

| 2-2. | 内部レイアウト観察                              | ... 11    |

| 2-3. | パッケージ断面構造解析                            | ... 12-26 |

| 3    | Si MOSFETチップ構造解析                       |           |

| 3-1. | 平面構造解析(OM)                             | ... 28-41 |

| 3-2. | 平面構造解析(SEM)                            | ... 42-50 |

| 3-3. | セル部 断面構造解析                             | ... 51-63 |

| 3-4. | チップ外周部 断面構造解析                          | ... 64-71 |

| 4    | Infineon製150V Si MOSFET(OptiMOS 5)との比較 | ... 72-73 |

| 5    | (※)関連特許紹介                              | ... 74-75 |

(※)関連特許: US20240145532A1

## 構造解析レポートからの抜粋

| T <sub>c</sub> = 25°C                        | Infineon OptiMOS 5<br>IPB060N15N5 | iDEAL Semi SuperQ<br>iS15M7R1S1C                                                    |

|----------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------|

| V <sub>dss</sub> (V)                         | 150                               | 150                                                                                 |

| Transistor active area AA (mm <sup>2</sup> ) |                                   |                                                                                     |

| R <sub>on</sub> (mΩ / V <sub>gs</sub> (V))   |                                   |                                                                                     |

| R <sub>on</sub> x AA (mΩ · mm <sup>2</sup> ) | 90                                | 60                                                                                  |

| Cell pitch P (μm)                            |                                   |                                                                                     |

| Cell structure features                      |                                   | Gate (Poly-Si) trench, ALD trench<br>(ALD layer doping (P type) on trench sidewall) |

Infineon製150V Si MOSFET (OptiMOS 5) との比較

(19) United States

(12) Patent Application Publication (10) Pub. No.: US 2024/0145532 A1

Jauregui et al. (43) Pub. Date: May 2, 2024

(54) COMBINED CHARGE BALANCE AND EDGE TERMINATION SURFACE PASSIVATION FOR A SEMICONDUCTOR DEVICE AND METHODS OF FABRICATING THE SAME

(52) U.S. CL.

CPC ..... H01L 29/0615 (2013.01); H01L 21/71

(2013.01); H01L 23/62 (2013.01)

(71) Applicant: IDEAL SEMICONDUCTOR DEVICES, INC., Bethlehem, PA (US)

(57) ABSTRACT

(72) Inventors: David Jauregui, Bethlehem, PA (US); Stanislav Soloviev, Breinigsville, PA (US); Philip Rutter, Bethlehem, PA (US)

A semiconductor device is provided that includes an epitaxial layer disposed on a semiconductor substrate, the epitaxial layer including an active region, in which at least one active element is formed, and an edge termination region, in which at least one edge termination structure is formed, the edge termination region being laterally adjacent to the active region. The semiconductor device further includes a charged layer disposed on an upper surface of the epitaxial layer, the charged layer covering at least a portion of the active region and extending laterally over at least a portion of the edge termination region. Active trenches may be formed in the active region, and at least one edge trench may be formed in the edge termination region. The charged layer may be formed on sidewalls of each of the active trenches and the edge trench using atomic layer deposition in a same processing step.

(21) Appl. No.: 18/464,686

(22) Filed: Sep. 11, 2023

### Related U.S. Application Data

(60) Provisional application No. 63/420,339, filed on Oct. 28, 2022.

### Publication Classification

(51) Int. Cl.

H01L 29/06 (2006.01)

H01L 21/71 (2006.01)

H01L 23/62 (2006.01)

### 関連特許概要 (US20240145532A1)

### 関連特許図面 (US20240145532A1)

ALD: Atomic Layer Deposition